Advanced Engineering Technology and

ISSN: 2090-9543

Application

VOLUME 3, ISSUES 2, 2014

www.egyptfuture.org/ojs/

# An Area Efficient Approach: Comparative Analysis of Multiplier Circuits

Amit Grover<sup>1,\*</sup>, Jyoti Gupta<sup>1</sup>, Keshav Kumar<sup>1</sup>, Neeti Grover<sup>2</sup> and Sumer Singh<sup>3</sup>

<sup>1</sup> Department of Electronics & Communication Engineering, S.B.S State Technical Campus Ferozepur, Punjab, India

<sup>2</sup> Department of Applied Sciences and Humanities, S.B.S State Technical Campus Ferozepur, Punjab, India

<sup>3</sup> Department of Electronics & Communication Engineering, Government Polytechnic College, Ferozepur, Punjab, India

Received: 5 Jan. 2014, Revised: 3 Mar. 2014, Accepted: 5 Mar. 2014 Published online: 1 May 2014

**Abstract:** Improvements in the performance of integrated circuits include scaling of transistor size and reduction of operating voltage. Smaller area and power dissipation have also taken care of for fabrication of high performance. Optimizing the power consumption, speed, area and delay of the multiplier are a major issue. In this article, the best solution to this problem is determined. As we know, Adders and Multipliers are key components of many high performance systems. By designing different multipliers, implementing their components is better to choose an option between CSL, DPL & CPL adders in fabricating different systems. This article focuses on the comparison between two algorithms for multiplication, Array and Wallace Tree. The implementation of these algorithms is performed by designing ( $4 \times 4and8 \times 8$ ) bit multiplier blocks in  $0.18\mu$  C MOS technology using EDA Tanner v.13 (evaluation version) framework tools. Furthermore, the 8-bit multipliers on GDI adder cells are compared using EDA Tanner. Multiplier design in this article provides the low power requirement and presents an area efficient approach. Moreover, number of transistors is also less as compared to CMOS for any design.

Keywords: CSL, DPL, CPL, GDI

## **1** Introduction

Digital multiplication is one of the most basic functions in a wide range of algorithms. Being the slowest element in the system, the performance of the system is determined by the performance of the multiplier block. Today multiplication is not only implemented with a sequence of addition, subtraction and shift operations. Many speed effective and power effective algorithms have been evolved depending upon the use in an application. From a delay perspective, algorithms place two constraints on multiplication: latency and throughput. Latency is the real delay of computing a function, a measure of how long after the inputs to a device are stable, is the final result available on the outputs. Throughput is a measure of how many multiplications can be performed in a given amount of time. Multiplier [1] in addition to a high delay block is also a major source of power dissipation, many algorithm are designed with the help of digital multiplication. So it is of great interest to identify and apply algorithms which has less delay as well as less power consumption of the multiplier i.e. which has smaller power delay product and fast processing.

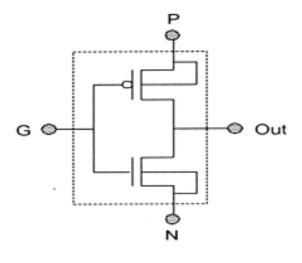

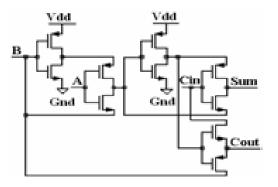

Bulks of both NMOS and PMOS are connected to N or P (respectively), so it can be arbitrarily biased at contrast with a CMOS inverter.

## 2 Preliminaries

A. Logic Equations for the Proposed Full Adders

The equations presented below can be stated as follows:

$$Sum = A \oplus B \oplus Cin \tag{1}$$

$$Sum = \overline{A} \oplus \overline{B} \oplus \overline{C}in \tag{2}$$

$$Sum = C\overline{in}(A \oplus B) + Cin(A\overline{\oplus}B)$$

(3)

$$Cout = A.(A \oplus \overline{B} + C\overline{in}(A \oplus B)) \tag{4}$$

Fig. 1: GDI basic cell [2]

Table 1: Various logic functions of GDI cell for different cell for different input configurations

| N   | Р   | G | Out                  | Function |  |  |

|-----|-----|---|----------------------|----------|--|--|

| '0' | В   | A | $\overline{A}B$      | Fl       |  |  |

| В   | 7'  | A | $\overline{A} + B$   | F2       |  |  |

| 7'  | В   | A | A + B                | OR       |  |  |

| В   | '0' | A | AB                   | AND      |  |  |

| С   | В   | A | $\overline{A}B + AC$ | MUX      |  |  |

| '0' | 'l' | A | $\overline{A}$       | NOT      |  |  |

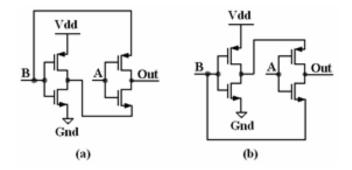

#### B. XOR and XNOR gates based on GDI cell

The XOR and XNOR gates based on GDI cells are applications of the GDI technique. As can be seen in Fig. 2, each of them requires only four transistors. Obviously, the proposed GDI XOR and XNOR gates use less transistors compared with the conventional CMOS counterparts [3].

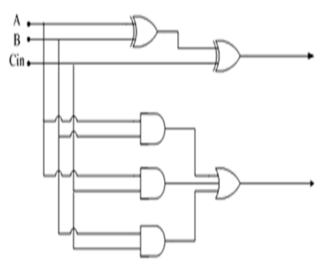

C. Full Adders Based on GDI XOR and XNOR Gates

According to the logic equations mentioned above and the GDI XOR and XNOR gates in Fig. 2,

Full adders can be, GDI based XOR full adder and GDI based XNOR full adder. Each of the two full adders includes 10 transistors. Figure 3 shows gate level design of full adder. Due to the advantages of GDI cell, this circuit still can achieve its benefit of low power consumption. This scheme also includes three modules.

Fig. 2: (a) GDI based XOR gate (b) GDI based XNOR gate [4]

Fig. 3: Gate level based of full adder [1]

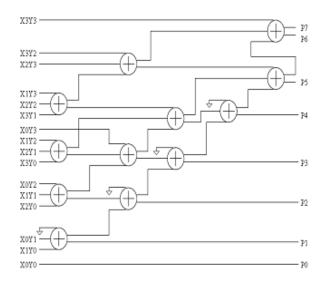

Figure 4 and 5 shows GDI based XOR and XNOR Full adders [5].

## **3 Multiplication Algorithms**

There are numerous multiplier [6] implementations, some of them are good in terms of power dissipation [7] and some have better performance in terms of delay [8]. In this section 8-bit array and tree multiplier algorithms are discussed.

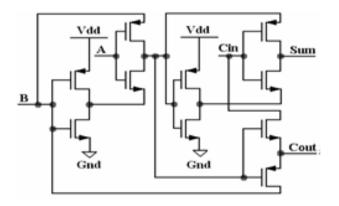

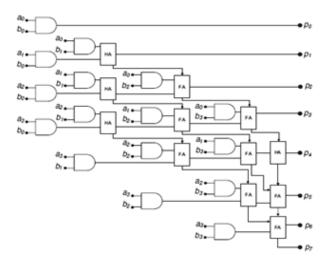

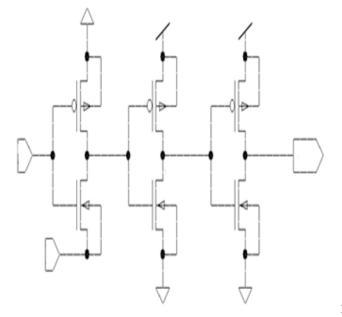

#### A. Array Multiplier

An  $n \times n$  array of AND gates can compute all the  $a_i b_i$ terms simultaneously. The terms are summed by an array of n[n-2]' full adders and 'n' half adders. The delay of this block is a function of the number of rows [9], O (n), which is a big improvement over the simple-minded scheme of using conventional adders for each row. Figure 6 shows  $4 \times 4$  array multiplier and Figure 7 shows  $4 \times 4$ Tree Multiplier. Figure 8 and 10 shows actual layouts of GDI based XOR and XNOR Full adders circuits whereas

Fig. 4: GDI Based XOR full adders

Fig. 5: GDI based XNOR full adder [3]

| PARAMET-<br>ERS          | CPL<br>ARRAY               | CPL<br>TREE                | CSL<br>ARRA<br>Y           | CSL<br>TREE                | DPL<br>ARRA<br>Y           | DPL<br>TREF                |

|--------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| Number of<br>Transistors | 1472                       | 1472                       | 1952                       | 1952                       | 2336                       | 2336                       |

| Power<br>Consumption     | 3.77 X<br>10 <sup>-4</sup> | 6.24 X<br>10 <sup>-4</sup> | 6.36 X<br>10 <sup>-4</sup> | 1.82 X<br>10 <sup>-4</sup> | 3.50 X<br>10 <sup>-4</sup> | 3.24 X<br>10 <sup>-4</sup> |

5.32 X 10<sup>-11</sup> 6.75 X 10<sup>-11</sup> 1.11 X 10<sup>-10</sup>

6.12 X 10<sup>-11</sup>

| Table 2: Comparative analysis of 8 | 8-bit multi | pliers |

|------------------------------------|-------------|--------|

|------------------------------------|-------------|--------|

Fig. 6: Block diagram of 4 × 4 array multiplier [11]

**Fig. 7:**  $4 \times 4$  Tree Multiplier

Figure 9 shows an AND gate. Optimizing [10] the power consumption, speed, area and delay of the multiplier are major issues, whose best solution is considered in this section.

4.11 X 10<sup>-11</sup>

1) Tree Multiplier

Delay

The advantage of Wallace tree is speed because the addition of partial products is O (log N) where N is the number of summands

## **4** Simulation and Comparison

1.01 X 10<sup>-10</sup>

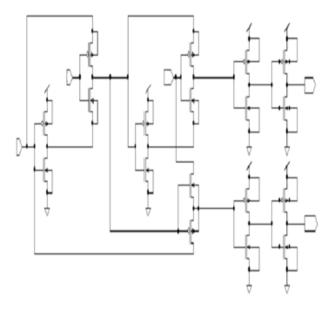

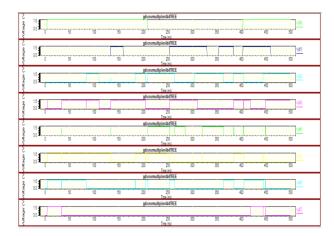

A. Simulation Environment: Array and tree multipliers based on GDI XOR and GDI XNOR adder cells are

simulated in EDA Tanner (Evaluation version). All the results are obtained in 180nm CMOS process technology.

Comparison: 8-bit array and tree multipliers are compared based on the parameters, delay and number of transistors. Comparative analysis of 8-bit multipliers using GDI based adder cells working at 400MHz is done with 8-bit CMOS multiplier as shown in the table 2.

## **5** Conclusions

Multiplier design in this paper work provides the low power requirement. It also presents an area efficient approach to low power, less number of transistors as

Fig. 8: GDI Based XOR full adder

Fig. 9: Schematic of AND Gate

B

Fig. 10: GDI Based XNOR full adders

Fig. 11: Output waveform of 8-Bit Tree Multiplier Using GDI XOR Based Adder Cells

compared to CMOS and DCVS for any design. 8-bit multipliers were designed in Tanner (Evaluation version) tool using 180nm and analysis of dynamic power dissipation, delay and area was done. The results in table 2 are at frequency 400MHz and load capacitance is 1pF. Channel length for both NMOS & PMOS is 180nm and width is 1790nm for PMOS & 699nm for NMOS transistor.

## **6** Future scope

As a future scope of the work, Power of the circuit can be further reduced if requirement of buffers in the circuit is avoided. Also, this technique can be compounded with other methods used such as using sleep transistors, dual threshold CMOS, dynamic threshold CMOS. This article work is based on combinational circuit design. Techniques can also be applied to sequential circuits. The

**Fig. 12:** Output Waveform of 8-Bit Array Multiplier Using GDI XOR Based Adder Cells

**Fig. 13:** Output waveform of 8-Bit Tree Multiplier Using GDI XNOR Based Adder Cells

work can be extended for the calculation of SPC as this article work mainly concentrates on the DPC of the total power consumption. In VLSI design CSL technique has very good scope for future because of less power consumption.

# References

- P. C. H. Meier, "Analysis and design of low power digital multipliers," Ph.D. dissertation, Citeseer, 1999.

- [2] A. Morgenshtein, A. Fish, and I. A. Wagner, "Gatediffusion input (gdi): a power-efficient method for digital combinatorial circuits," *Very Large Scale Integration (VLSI)*

Fig. 14: Output waveform of 8-Bit Array Multiplier Using GDI XNOR Based Adder Cells

Fig. 15: Output waveforms from p0 to p7 of 8-Bit Tree Multiplier Using GDI XOR Based Adder Cells

Systems, IEEE Transactions on, vol. 10, no. 5, pp. 566–581, 2002.

- [3] D. Wang, M. Yang, W. Cheng, X. Guan, Z. Zhu, and Y. Yang, "Novel low power full adder cells in 180nm cmos technology," *Industrial Electronics and Applications*, vol. 12, pp. 430–433, 2009.

- [4] A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, "Low-power cmos digital design," *IEICE Transactions on Electronics*, vol. 75, no. 4, pp. 371–382, 1992.

- [5] V. Adler and E. G. Friedman, "Delay and power expressions for a cmos inverter driving a resistive-capacitive load," *Analog Integrated Circuits Signal Processing*, vol. 14, pp.

| S              |                        |    |     |     |    | divoribi/REE                  |           |                |      |    |                              |

|----------------|------------------------|----|-----|-----|----|-------------------------------|-----------|----------------|------|----|------------------------------|

| 8              |                        |    |     |     |    |                               |           |                |      |    |                              |

| Į.             |                        | 61 | 10  | 10  | 20 | 20<br>Total                   | 300       | 22             | -0   | -0 | 500                          |

| giustaffee     |                        |    |     |     |    |                               |           |                |      |    |                              |

| 8              |                        |    |     |     | -  |                               |           |                |      |    |                              |

| Į.             |                        | 5  | 100 | 150 | 20 | 23<br>Teripi                  | 300       | 35             | 40   | 8  | 500                          |

| Ś              | 172 25.<br>ptostb.0762 |    |     |     |    |                               |           |                |      |    |                              |

| ş              | 12                     |    |     |     |    |                               |           |                |      |    | and the second second        |

| ų.             |                        | 5  | 100 | 151 | 20 | 23<br>Top bit                 | 300       | 35             | -0   | 6  | 500                          |

| Ś              |                        |    |     |     | 1  | disorbalifiete                |           |                |      |    |                              |

| 9              |                        |    |     |     |    |                               | ******    | ************** |      |    |                              |

| ų.             |                        | 3  | 10  | 10  | 20 | 20<br>Topici                  | 300       | 33             | - 40 | 6  | 500                          |

| Ş              |                        |    |     |     |    | example and the second second |           |                |      |    |                              |

| 9              |                        |    |     |     |    |                               |           |                |      |    |                              |

| ų,             |                        | 3  | 100 | 15  | 20 | 20<br>Torbi                   | 300       | 51             | 0    | 6  | 500                          |

| Ş              |                        |    |     |     |    | doorbi/REE                    |           |                |      |    |                              |

| ĝ              |                        |    |     |     |    |                               | <u> </u>  |                |      |    | <u>i (1</u>                  |

| vo <b>u</b> r. |                        | 5  | 100 | 150 | 22 | 23                            | 300       | 20             | 0    | 6  | 50                           |

|                |                        |    |     |     |    |                               |           |                |      |    |                              |

| ş              |                        |    |     |     | ÷  |                               |           |                |      |    | <u> 194</u>                  |

| ų.             | . 0                    | 5  | 100 | 151 | 20 | 23<br>Ten hel                 | 300       | 351            | -00  | -8 | 500                          |

| ξ              |                        |    |     |     |    | disorbalitREE                 |           |                |      |    |                              |

| 0              |                        |    |     |     |    |                               | ********* | ********       |      |    | and the second second second |

| ACM.           |                        | 5  | 100 | 5   | 20 | 20<br>Imini                   | 300       | 33             | -0   | 6  | 500                          |

**Fig. 16:** Output waveforms from p8 to p15 of 8-Bit Tree Multiplier Using GDI XOR Based Adder Cells

**Fig. 17:** Output waveforms from p0 to p7 of 8-Bit Array Multiplier Using GDI XOR Based Adder Cells

29-39, 1997.

- [6] C. S. Wallace, "A suggestion for a fast multiplier," *Electronic Computers, IEEE Transactions on*, vol. 10, no. 1, pp. 14–17, 1964.

- [7] K.-S. Yeo and K. Roy, Low voltage, low power VLSI subsystems. McGraw-Hill, Inc., 2004.

- [8] T. Sakurai, "Closed-form expressions for interconnection delay, coupling, and crosstalk in vlsis," *Electron Devices*, *IEEE Transactions on*, vol. 40, no. 1, pp. 118–124, 1993.

- [9] N. Ravi, A. Satish, T. J. Prasad, and T. S. Rao, "A new design for array multiplier with trade off in power and area."

Fig. 18: Output waveforms from p7 to p15 of 8-Bit Array Multiplier Using GDI XOR Based Adder Cells

International Journal of Computer Science Issues (IJCSI), vol. 8, no. 3, pp. 533–537, 2011.

- [10] S. Devadas and S. Malik, "A survey of optimization techniques targeting low power vlsi circuits," in *Proceedings* of the 32nd annual ACM/IEEE Design Automation Conference. ACM, 1995, pp. 242–247.

- [11] N. Anuar, Y. Takahashi, and T. Sekine, "4 × 4-bit array two phase clocked adiabatic static cmos logic multiplier with new xor," in VLSI System on Chip Conference (VLSI-SoC), 2010 18th IEEE/IFIP. IEEE, 2010, pp. 364–368.

Amit Grover became a Member (M) of Association ISTE in 2006, a Senior Member (SM) of society SELCOME in September 2009, and a Project-In charge (PI) in august 2011 and in September 2012. The author place of birth is Ferozepur, Punjab, India on 27th, September 1980.The author received his M.

Tech degree in Electronics & Communication Engineering from Punjab Technical University, Kapurthla, Punjab, India in 2008 and received his B. Tech degree in Electronics and Communication Engineering from Punjab Technical University, Kapurthala, Punjab, India in 2001. Currently, he is working as an Assistant Professor in Shaheed Bhagat Singh State Technical Campus, Ferozepur, Punjab, India. The author is a Reviewer of many Reputed International Journals. His area of interest includes signal processing, MIMO systems, Wireless mobile communication; high speed digital communications, 4G Wireless Communications and VLSI Design.

**Jyoti Gupta** received her B.Tech degree in ECE in 2012 from Baba Farid College of Engineering and Technology, Affiliated to PTU, Kapurthala, Punjab. Her place of birth is Ferozepur, Punjab, India on 20th April, 1990. At present she has been doing her research work

under the guidance of Mr. Amit Grover, Assistant Professor, Department of ECE, Shaheed Bhagat Singh State Technical Campus, Moga road, Ferozepur, India.

Keshav Kumar is pursuing Master of Technology his Electronics in the area of and Communication Engineering under the supervision of Mr. Amit Grover, Assistant Professor, Department of Electronics & Communication Engineering, Shaheed Bhagat Singh State Technical Campus (Established

by Govt. of Punjab) Moga road, Ferozepur, Punjab, India. The author place of birth is Banmankhi, Distt. Purnea, Bihar India on 15th, April 1989. Keshav Kumar received his B. Tech degree in the area of Electronics & Communication Engineering in 2011 From Baba Hira Singh Bhattal Institute of Engineering & Technology (Established by Govt. of Punjab) Lehragaga, Distt-Sangrur, Punjab, India.

**Neeti Grover** received her master degree in Applied Sciences from Guru Nanak Dev University, Amritsar, and Punjab, India in 2007 and received her Bachelors degree from Guru Nanak Dev University, Amritsar, Punjab, India in 2004. Her place of birth is Jallandhar, Punjab,

India on 29th, December 1983. Currently, she is working as an Assistant Professor in the department of Applied Sciences and Humanities in Shaheed Bhagat Singh State Technical Campus (Poly Wing), Ferozpur, Punjab, India.

**Sumer Singh** the author place of birth is Ferozepur, Punjab, India on 15th, August 1985. The author received his M.Tech degree in Electronics and Communication Engineering from Punjab Technical University, Kapurthla, Punjab, India in 2013 and received his B.Tech degree in Electronics and

Communication Engineering from Punjab Technical University, Kapurthala, Punjab, India in 2010. Currently, he is working as a Lecturer in Department of Electronics & Communication Engineering, Government Polytechnic College, Ferozepur, Punjab India. His area of interest includes Wireless Communication Network, Mobile Ad Hoc Network, Wireless Sensor Network and VLSI Design.