FP 1 226

MILITA ,RY TECHNICAL COLLEGE CAIRO-EGYPT

FIRST INTERNATIONAL CONF. ON ELECTRICAL ENGINEERING

### A PWM DC TO AC CONTROLLED INVERTER WITH VARIABLE FREQUENCY

### A. A. Heggo<sup>\*</sup>

### ABSTRACT

The inverter controlled by a microprocessor is applicable in many industrial applications. The two main parameters which are variable are amplitude and frequency. This paper describes an efficient and powerful modulation method. This technique permits the formation of the output wave easily and efficiently by means of PWM. This proposed inverter control scheme allows improvements on the AC drive performance, while using simple dedicated hardware. The proposed scheme would be attractive for modern applications that require a non-standard wave form. This paper presents the mathematical relation between the distortion, switching frequency and operating point, and the system parameters. The simulation results are obtained and commented upon.

#### NOMENCLATURE

| A                | - | amplifier gain                  |

|------------------|---|---------------------------------|

| С                | = | capacitance of L - C filter     |

| E                | = | harmonic voltage rms value      |

| I                | = | average current                 |

| $I_{dc}$         |   | dc output current               |

| Idq              | = | Idc component in quadratur axis |

| n                |   | higher harmonic degree          |

| Pout             |   | output dc power                 |

| R                | = | resistance of input filter      |

| T,               | = | switching interval              |

| u                | = | commutation overlap zigle       |

| V                | = | average voltage                 |

| $V_{dc}$         |   | actual output dc voltge         |

| V <sub>dco</sub> | = | average output dc vatage        |

|                  |   |                                 |

A service and a se

a s N 0

$V_{dq} = V_{dc}$  component in quadrature axis

- $V_i$  = input dc voltage

- $V_L$  = lower value of dc voltage

- $V_m = maximum ac voltage$

- $V_{o}$  = output ac voltage

- $V_{u}$  = ultimate value of dc voltage

- W = pulsation frequency

- $\alpha$  = firing angle

- $\Theta$  = displacement angle

### INTRODUCTION

Digital inverters are used today in many industrial applications. These applications frequently need variable speed, amplitude and frequency.[1] The inverter enabling the formation of arbitrarily shaped reference time function of output current or voltage, such as servo motor drives, uninterrupted power supply (UPS) and system compensation of reactive and deformation power.[2]

The harmonics and reactive power instantaneous compensators demand a high quality inverter scheme that can be considered as a kind of power amplifier.[3] Pulse width modulation techniques are presently the most popular and economic methods for electric power conversion.[4] Normally the electronic control circuit drives and inverter power drives are used for generating pulse width modulated terminal voltage necessary for providing the desired wave shape to the lead.[5]

Regarding the modulator there are different sinusoidal based PWM generation methods such as sinusoidal modulation, distortion minimization and harmonic elimination.[6] There are many studies which have been published on the study of harmonic cancellation on the basis of micro processor technique.[7] All methods of PWM generation have the common characteristic that the modulator needs information in advance about wave shape, frequency and amplitude to pulse pattern.[8] Generally for recent applications, the flexibility in forming sinusoidal or non-sinusoidal waves with high frequency require a complex modulator structure.[9] By using a microprocessor approach however it is possible to get an easier structure and a faster response.[10] This study gives an evaluation of a recent structure of an inverter. The simulation results are obtained at different load conditions.[11]

### PULSE WIDTH MODULATION MODES

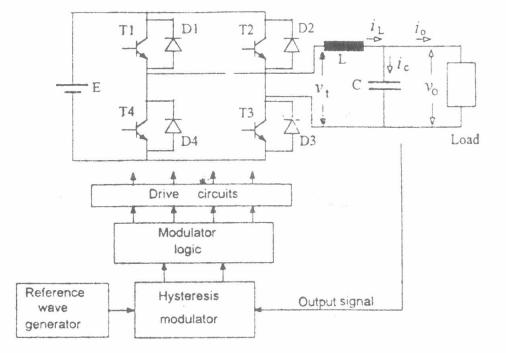

Considering the inverter circuit as shown in Figure 1 the following pairs of devices may be conducting T1, T2, T3 and T4 and also D1, D2, D3 and D4 so there are three possible levels for the terminal voltage, +E, 0 and -E.

In bipolar mode the inverter module activates the inverter switches to produce either positive or negative voltage at the inverter terminal. The positive voltage is obtained by switching the diagonally opposite power devices T1 and T3 simultaneously while the negative is

EP.1 228

Fig. 1 Block Diagram of PWM Controlled Inverter

obtained by switching T2 and T4.

In the case of unipolar mode the modulator switches the inverter terminal between the two voltage levels +E and 0 during the positive half and -E and 0 during the negative half. There is a very important effect on the wave form shape that is a time constant of the load. This means that the output wave shape may not follow the reference wave. In addition the switching frequency demand from the inverter is unknown and may exceed the inverter switching capacity. Moreover the load and filter parameters affect the controllability of the high frequency ripples.

#### THE MATHEMATICAL MODELLING [12]

The voltage and current equations in direct axis, quadrature axis are:

$$V_{dq} = V_d + jV_q \tag{1}$$

$$I_{dq} = I_d + jI_q \tag{2}$$

The desired current reference that:

EP.1 229

- results from input/output balance

- produce unity input power factor

- results in input sinusoidal currents

$$I_{dref}(t) = \frac{2}{3} \frac{V_d(t)}{V_d^2(t) + V_q^2(t)} P_{cut}(t)$$

(3)

$$I_{qref}(t) = \frac{2}{3} \frac{V_q(t)}{V_d^2(t) + V_q^2(t)} P_{cut}$$

(4)

where:

$$P_{cut} = V_{dc} I_{dc} + K_1 (V_{dcref} - V_{dc}) + K_2 (V_{dcref} - V_{dc}) dt$$

(5)

This represents the power output requirement at input (t) and is computed as the combination of load feed forward and P-1 controller of dc bus voltage error.

The delay period is to be passed before the control action is applied. This could cause the regulator to become oscillatory. This action may be done at low frequency switching. So the integral term corrects this problem. The relation between instant voltage and control voltage in rectifier side is as follows:

$$V'_{qdref}(t) = V_{qd}(t) - \frac{L(I_{qdref} + 2T_s) - I_{qd}(t + T_s)}{T_s}$$

(6)

where:

$$I'_{qd}(t+t_s) = I_{qd}(t) + [V_{qd}(t) - V_{qd}(t-T_s)] \frac{T_s}{L}$$

(7)

Equation (7) is calculated from instantaneous input voltage and control voltage  $V_{qd}$  supposing that  $V_{dc}$  is constant.

Also the dc output voltage from ac input voltage is:

Proceeding of the 1<sup>st</sup> ICEENG conference, 24-26 March, 1998.

$V_{dc} = V_{dco} + \Sigma \sqrt{2} E \sin(\theta + \alpha)$ (8)

and

$$E = \frac{V_{dco}}{\sqrt{2}(n^2 - 1)} \sqrt{u} \tag{9}$$

$$u = 2\cos^{2}\alpha + (n^{2} + 1)\sin^{2}\alpha + (n^{2} - 1)\sin^{2}(\alpha + u) + \cos nu[2\cos\alpha\cos(\alpha + u) + 2n^{2}\sin\alpha\sin(\alpha + u)]$$

(10)

Equations (8) and (9) represent the output dc voltage and harmonic voltage. On the other hand the equations of the dc-ac side will be:

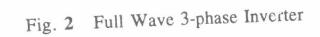

$$V_i = \frac{T_2}{T} \frac{VL + Vu}{2} \tag{11}$$

$$V_{o} = \frac{T_{1}}{T} \frac{VL + Vu}{2} \tag{12}$$

EP.1 230

Proceeding of the 1<sup>st</sup> ICEENG conference, 24-26 March, 1998.

EP.1 231

(13)

$V_o = AV_i$

destablistic kur i i menetnep Ditter

where:

$$T_1 = Rc \frac{Vu - VL}{V_o} \tag{14}$$

$$T_2 = Rc \frac{Vu - VL}{V_o} \frac{V_i}{V_o}$$

(15)

$$T = \frac{RC}{2} \frac{Vu^2 - VL^2}{V_1^2}$$

(16)

$$A = \frac{Vu + VL}{2V_i} - 1 \tag{17}$$

The equation (13) represents the relation between input dc voltages and output ac voltage.

## DESIGN CONSIDERATION

As shown in Figure 2 the voltage reversal in both sides dc or ac can be made. This gives the circuit the capability of two quadrant operation. The four quadrant operation can be achieved by providing current reversible paths to the circuit. Generally, the upper limit of input voltage Vu is larger than the source voltage. But the lower limit of input voltage is kept as small as possible to maximise the energy transfer by minimising the energy returned from the output filter. The PWM pattern is determined at every sampling instant by the microprocessor, based on the output measurements and the references. A low harmonic distortion sinusoidal output is obtained by using a feedback control technique. The control rule is very simple and requires two measurements and two multiplications at the start of each sampling interval. This scheme provides very good voltage regulation and very fast response for load disturbances and non-linear load. Also to increase the flexibility in forming the sinusoidal wave a digital method for generating the PWM pattern must be used.

### SIMULATION RESULTS

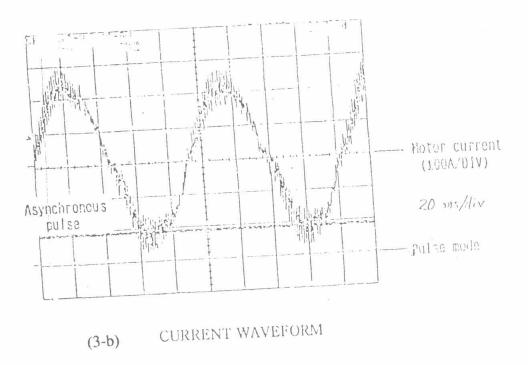

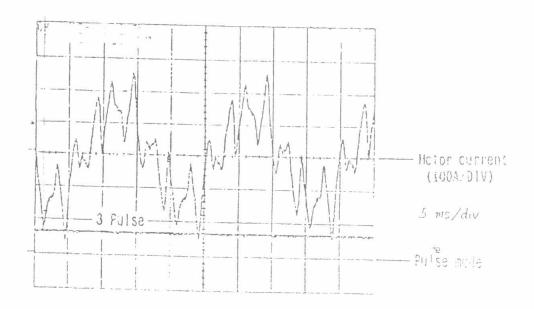

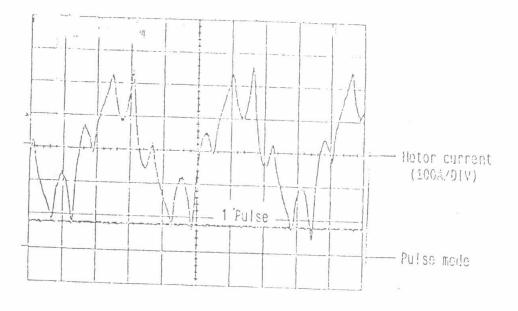

A computer model program was prepared to study the complete behaviour of the converter. This programme is convenient for small and large signal transients. During the start-out there is a maximum limit in the increasing of voltage gain, achievable for each cycle. The results obtained are shown in Figures (3), (4) and (5).

The electrical data is:

| * ac side 1 | <ul> <li>number of phases</li> <li>input voltage</li> <li>input frequency</li> <li>Type of rectifier</li> </ul>                                             | = 3<br>= 380 V<br>= 50 Hz<br>= 12 - pulse mode                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| * dc side   | <ul> <li>rated voltage</li> <li>average voltage value</li> <li>rated current</li> </ul>                                                                     | = (500 - 900V)<br>= 750V<br>= 4000A                                                                |

| * ac side 2 | <ul> <li>number of induction motor</li> <li>rated voltage</li> <li>rated power</li> <li>rated current</li> <li>frequency</li> <li>slip frequency</li> </ul> | rs/car = 4 motors<br>= 550V<br>= 115Kw<br>= (129 - 156)A/inverter up to +17%<br>= up 70Hz<br>= 1.7 |

### CONCLUSION

The proposed scheme for a digital inverter is presented and discussed in this paper. The derivation of equations is obtained. The simulation results are introduced and commented upon. The model is convenient for many industrial applications.

This paper has verified an effective means of controlling the inverter power circuit to produce output that follows any arbitrary reference wave to eliminate the dependency of the controlled state on load disturbances.

### REFERENCES

- 1. "The Thyristor and its Application", Anthony Grefin and R.S.Ramshaw, Department

- of Electrical Engineering, University College of Swansea, 2nd edition 1973

- "Formation of Output Current of Voltage Fed Inverter with Application of Alter-polar Modulation", European Conference of Power Electronic and Application, pp 229-235, 1985

Proceeding of the 1<sup>st</sup> ICEENG conference, 24-26 March, 1998.

EP-1 233

- "Compensator for Harmonics and Reactive Power Using Static Induction Thyristors", M.Kohata and A.Nabque, European Conference of Power Electronic and Application, pp 1265-1273, 1987

- 4. "Microprocessor Control of DC/AC Static Convertor", C.M.Penalver and M.Martinez, IEE Transaction on Industrial Electronics, Vol. IE-33 No.3 pp 186-191, 1985

- Adaptive Harmonic Control in PWM Inverter with Fluctuating Input Voltage", J.T.Lee and Y.T.Sun, IEE Transaction on Industrial Electronics, Vol. IE-33 No.1 pp 92 - 99, 1986

- "A Control Strategy for Reference Wave Adaptive Current Generation", R.G.Palanippan and J.Vithayathil, IEEE Transaction on Industrial Electronics and Control Instrumentation, Vol. IE-27, No.2, pp 92-96, May 1980

- 7. "Application of Power Transistor to Residential and Intermediate Rating Photo-voltaic Array Power Conditions", R.L.Steigerwald, A.Ferraro and G.Turnbull, IEEE Transaction on Industrial Application, Vol. IA-19, No.2, pp 254-269, May 1963

- "Generalised Techniques of Harmonic Elimination and Voltage Control in Thyristor", H.Patel and R.G.Hoft, Part I, IEEE Transaction on Industrial Application, Vol. IA-9, No.3, pp 310-317, May 1974

- 9. "Low Frequency Characterization of PWM Converter", J.W.Wilson and Y.A. Yeamans, IEEE Meeting Annual, pp 967-973, 1976

- 10. "A General Unified Approach to Power Modelling Switching Converter Power Stages", R.D.Middlebrook and S.Cuk, IEEE PESC pp18-14, 1976

- 11. Influence of the Control Principle on a High Voltage Inverter System for Reduction of Traction Transformer Weight", S.Astlund, European Conference on Power Electronic and Application, pp 561-566, Aachen 1989

- "An Improved Deadbeat Rectifier regulator Using a Neural Net Predictor", F.Kamran and T.G.Habetler, IEEE Transaction on Power Electronics, Vol. 10, No. 4, pp 504-510, July 1995

350 V/div

100 ms/div

# (1-a) VOLTAGE WAVEFORM

Fig. 3 The voltage and current waveforms under the "Asynchronous Pulsation Mode".

0

350 V/div

2 ms/div

### (5-a) VOLTAGE WAVEFORM

(5-b) CURRENT WAVEFORM

Fig. 4 The voltage and current waveforms under the "3 Pulse Modulation Mode".

| <br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |              |                | (* *** |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------------|--------|

| The state of the s | <br>       |              | Pris 0-44024-2 | • •    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | <br>Trager I |                | * * *  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ا<br>مقارد |              |                |        |

350 V/div

2 ms/div

(5-a) VOLTAGE WAVEFORM

(6-b) CURRENT WAVEFORM